The Value of Hardware-Assisted Verification

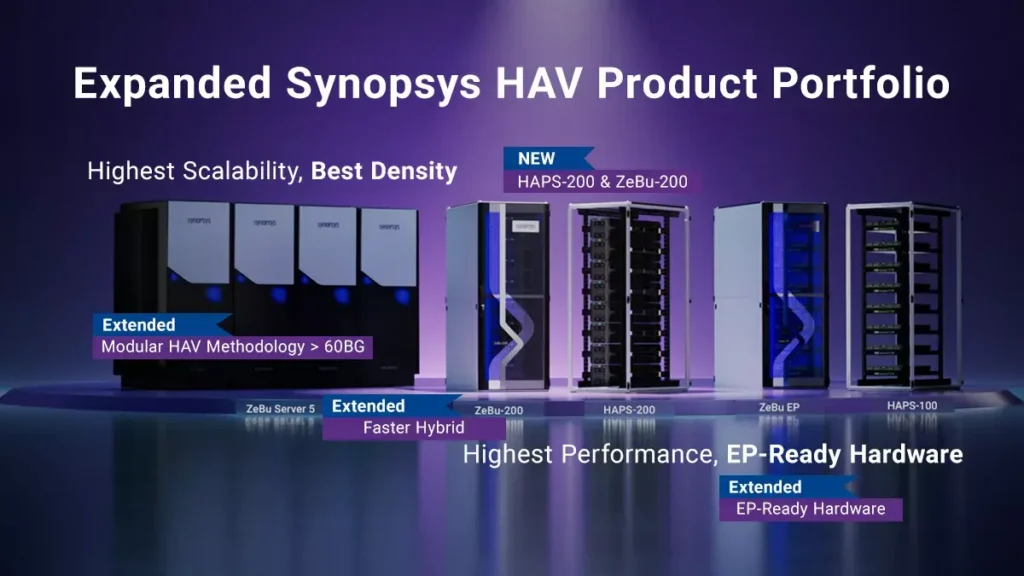

Are traditional simulation-based verification methods sufficient to meet the demands of modern chip development? As the electronics industry faces “escalating silicon complexity in software defined systems”, Synopsys asserts that hardware-assisted verification (HAV) is no longer optional, it’s “mandatory”. With soaring gate counts, increasingly complex software workloads and tighter development cycles, design teams need faster, more scalable verification solutions. To address this, Synopsys has expanded its industry-leading HAV portfolio with a new generation of high-performance emulation and prototyping platforms.

Based on the AMD Versal™ Premium VP1902 adaptive SoC, the new ZeBu-200 and HAPS-200 deliver higher performance, improved compile times and enhanced debugging capabilities, offering greater scalability and efficiency compared to their predecessors, HAPS-100 and ZeBu EP. Built on Synopsys Emulation and Prototyping (EP) Ready hardware, these solutions are specifically engineered to tackle the challenges of next-generation chip design and verification workflows in the “AI-driven era”.

“With the industry approaching 100s of billions of gates per chip and 100s of millions of lines of software code in SoC and multi-die solutions, verification of advanced designs poses never-before seen challenges,” said Ravi Subramanian, chief product management officer, Synopsys. “Our new systems deliver the highest HAV performance while offering the ultimate flexibility between prototyping and emulation use.”

Introducing ZeBu-200 & HAPS-200 powered by AMD Versal Premium VP1902 Adaptive SoC

ZeBu-200: High Performance Emulation

According to the official announcement, ZeBu-200 delivers a significant performance boost, offering up to 2x higher emulation performance compared to its predecessor. Debugging is also enhanced, with up to 8x better debug bandwidth, enabling faster issue resolution. Its scalability reaches up to 15.4BG, providing up to 6x greater capacity for large-scale designs. Faster compile times help reduce verification bottlenecks, while improved trace memory enables at-speed capture of design waveforms and traces. Additionally, ZeBu-200 is fully compatible with HAPS ProtoCompiler, ensuring seamless integration for prototyping workflows.

| Key Features | ZeBu-200 Specification* |

|---|---|

| Capacity | Scalable up to 15.4 BG |

| Software | ZeBu Software |

| Language Support | Verilog, VHDL, SystemVerilog, EDIF gate-level, SystemVerilog assertions, SystemC |

| Use Modes | Supports hybrid emulation with virtual prototypes, accelerates simulation, enables power analysis and allows for synthesizable test benches. Provides transaction-based and in-circuit emulation, virtual host/device environments and tester setups |

| Low Power Verification | Supports IEEE 1801 UPF for low-power verification, including power domains, gating, isolation and retention |

*Specs sourced from the official ZeBu-200 data sheet

HAPS-200: Next-Gen Prototyping

The HAPS-200 next-generation prototyping system delivers up to 2x higher performance than its predecessor, according to the recent Synopsys launch. With up to 4x greater debug bandwidth, it enables faster and more efficient issue resolution. Designed for high-speed operation, HAPS-200 can achieve speeds of up to 400+ MHz, making it ideal for interface protocol systems. Its scalability allows for configurations ranging from a single FPGA to multi-rack setups, supporting capacities of up to 10.8BG. For streamlined emulation workflows, it is fully compatible with ZeBu software utilizing EP-Ready Hardware.

| Key Features | HAPS-200 Specification* |

|---|---|

| Capacity | 6 FPGAs per system, up to 32 systems |

| FPGA | AMD Versal™ Premium VP1902 Adaptive SoC |

| Deployment | Rack or Desktop |

| Connectivity | Direct Connect Architecture |

| Power | Supply: 220V | Max Consumption: 2kW |

*Specs sourced from the official HAPS-200 data sheet

Key Takeaway: Enhanced Performance, Better Debugging & Increased Scalability

With high-performance prototyping capabilities, HAPS-200 enables early software development, system validation and hardware-software integration. In parallel, the ZeBu-200 emulation system supports thorough verification of complex designs with vastly improved debug capabilities.

Together, these solutions are already proving a valuable addition to industry-leading design and verification teams’ toolsets, enhancing performance, scalability and efficiency across workflows with seamless integration for a diverse range of use cases.

Industry Support for Synopsys HAV solutions

Early industry support for the Synopsys HAV portfolio expansion has been overwhelmingly positive:

Commenting on the launch, Alex Starr, Corporate Fellow at AMD, stated:

“Extending the modular HAV capabilities to the ZeBu Server 5 platform provides a scalable emulation roadmap to address the complex challenges of validating AMD’s largest next-generation devices. AMD has used ZeBu EP solutions for fast emulation with software workloads for a number of years. The Synopsys EP-Ready Hardware concept has allowed us to switch on demand, as a design matures, to a prototyping use case and significantly increase workload throughput. ZeBu-200 and HAPS-200 EP-Ready systems will enable further performance improvements to accelerate design verification and software validation.”

Narendra Kondra, VP of Hardware Engineering at NVIDIA, said:

“With the increasing market requirements for handling large AI computational data sets driving the need for enormous GPU and CPU computational power, the development time for NVIDIA’s next generation AI systems have become highly compressed to a yearly release cycle, necessitating best-in-class prototyping solutions. Synopsys HAPS-200 offers the fastest prototyping speed in the industry. The 50 MHz performance we have been able to achieve with HAPS-200 has been key to boosting productivity of our software development teams.”

Albert Huntington, VP of Platform Execution at SiFive, added:

“With its EP-Ready hardware, HAPS-200 offers us an FPGA platform to do full system emulation for reference platforms that scale from small microcontrollers all the way to large scale data center designs.”

Availability & Next Steps

Both the Synopsys HAPS-200 prototyping system and ZeBu emulation system are now available for early access customers.

As silicon design complexity continues to grow, these solutions will likely play a crucial role in accelerating next-gen semiconductor verification, driving efficiency and increasing productivity for teams pioneering innovation across the industry.

Learn more:

- Explore the official announcement & resources for more on these advanced HAV solutions from Synopsys

- Read this blog article for valuable insights into the future of chip design and hardware-assisted verification

Follow us on Linkedin and stay tuned for our upcoming article, where we dive deeper into hardware-assisted verification.